无需光刻机制造芯片?纳米压印技术在电子线路板制造中的潜力与现实

随着全球芯片制造行业对极紫外光刻(EUV)设备的依赖日益加深,其高昂成本与技术壁垒促使业界寻找替代方案。纳米压印技术(Nanoimprint Lithography, NIL)作为一种潜在的革命性工艺,引发了广泛关注:它是否真能绕开复杂的光刻机,成为芯片及电子线路板制造的新路径?

纳米压印技术的基本原理

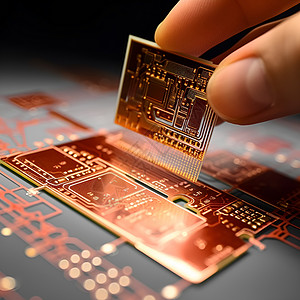

纳米压印技术本质上是一种“盖章”式的微纳图形转移工艺。它通过预先制备的、带有纳米级图案的模板(通常由石英或硅材料制成),在涂有光刻胶或其他可固化材料的基片(如硅晶圆或线路板基材)上直接压印,形成精细的电路图形。与光刻技术利用光学投影和化学显影不同,纳米压印依靠物理接触和机械成型,理论上无需复杂的光源系统和镜头组,设备结构相对简化。

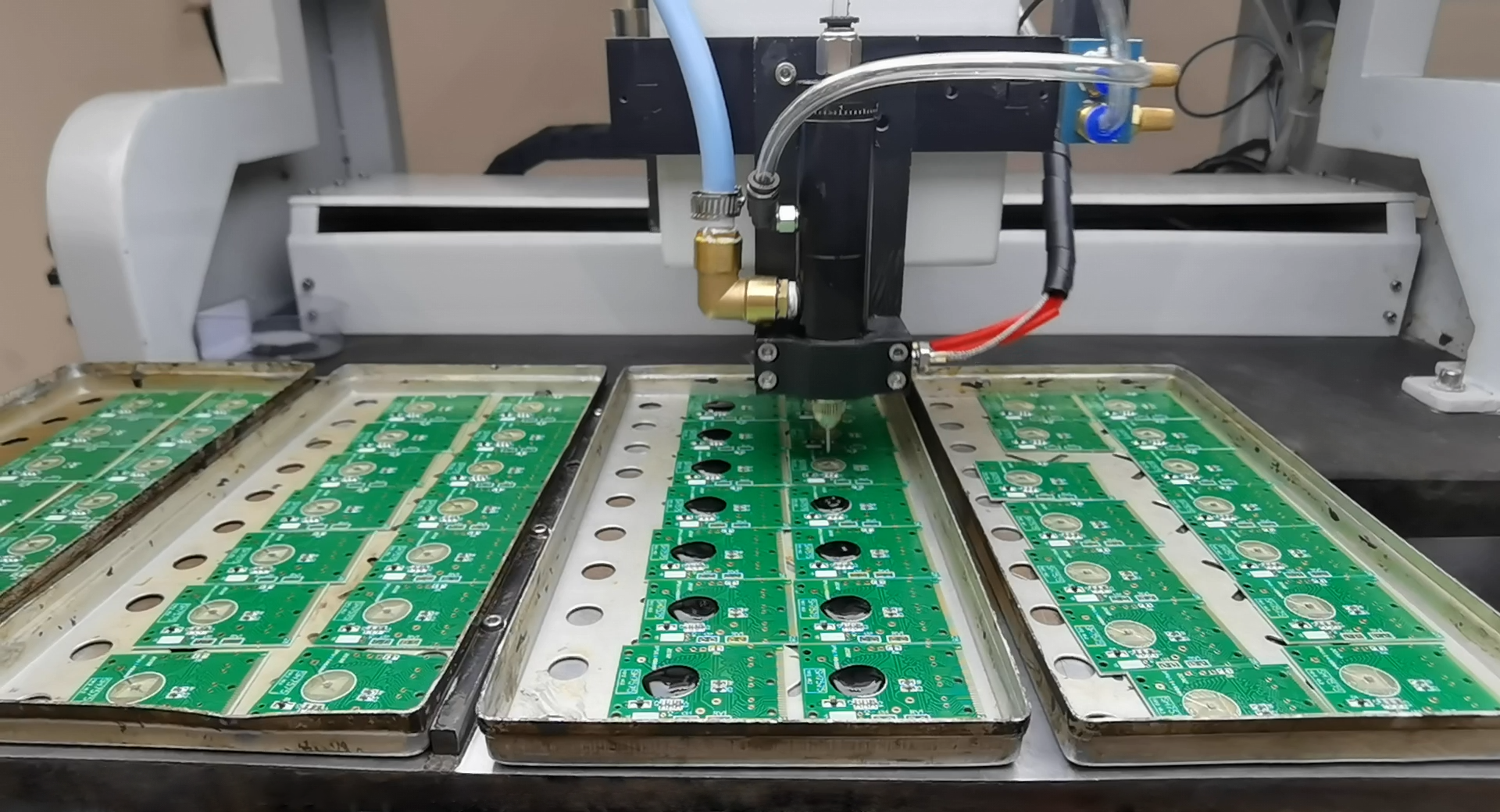

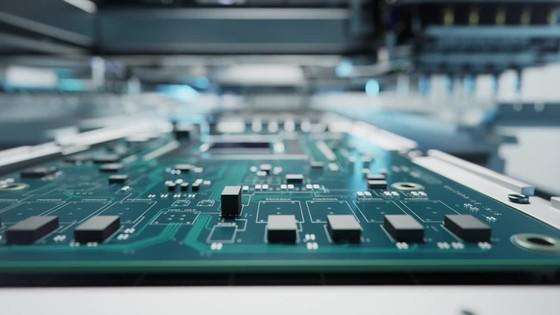

在电子线路板制造中的应用与优势

在传统印刷电路板(PCB)和高密度互连(HDI)板制造中,纳米压印技术已展现出独特价值:

- 高分辨率与低成本潜力:对于线宽在微米至亚微米级别的先进封装基板、柔性电子线路,纳米压印能实现高精度图形化,且设备投资和运营成本可能低于同类光刻系统。

- 材料适应性广:该技术可在聚合物、玻璃甚至柔性衬底上直接压印,适用于射频器件、传感器、显示面板等非硅基电子产品的线路制造。

- 节能与环保:省略了光刻中的多步化学处理,减少了溶剂使用和废弃物产生。

技术挑战与“靠谱性”审视

尽管前景诱人,但纳米压印若要替代光刻机成为芯片制造的主流技术,仍面临严峻挑战:

- 模板制作与寿命:高精度模板本身仍需依赖电子束光刻等工艺制备,成本不菲;且在多次压印后易磨损或污染,影响量产稳定性。

- 套准精度缺陷:对于多层堆叠的芯片结构,纳米压印在层间图案对齐(套准)精度上目前难以达到EUV光刻的亚纳米级水平,限制了其在先进制程(如7纳米以下)的应用。

- 产能与吞吐量:接触式压印可能带来效率瓶颈,大规模晶圆生产中的均匀性和速度仍有待提升。

- 缺陷控制难题:压印过程中产生的气泡、残留层不均等缺陷,对芯片良率构成风险。

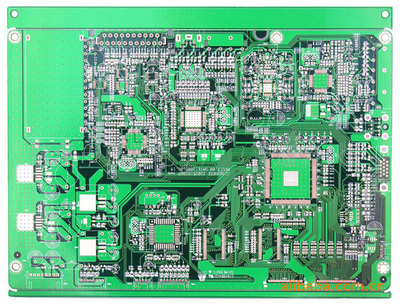

现实定位与未来展望

当前,纳米压印技术更可能扮演“补充者”而非“颠覆者”的角色:

- 在特定领域率先落地:如光子芯片、生物传感器、微纳光学元件等对分辨率要求高、但无需极端微缩的领域,纳米压印已实现商用。

- 与现有工艺融合:在先进封装、三维集成技术中,纳米压印可用于重新布线层(RDL)或硅通孔(TSV)的图形化,作为光刻的补充工艺。

- 持续技术突破:研究机构正致力于开发步进式纳米压印、无模板自组装等变体技术,以改善套准精度和产能问题。

结论

纳米压印技术为电子线路板及芯片制造提供了一条值得探索的差异化路径,尤其在非硅基、多集成场景中具有显著优势。要完全取代光刻机应对摩尔定律的尖端挑战,它仍需在精度、可靠性和量产能力上实现跨越。短期内,这项技术更可能以“并行方案”的形式,在特定应用场景中开花结果,推动半导体产业生态的多元化发展。对于行业而言,保持技术路线的开放与创新,才是应对未来不确定性的关键。

如若转载,请注明出处:http://www.chinamjdz.com/product/3.html

更新时间:2026-04-12 13:25:56